# 54\$/74\$137

### 1-OF-8 DECODER/DEMULTIPLEXER

(With Input Latches)

**DESCRIPTION** — The 'S137 is a very high speed 1-of-8 decoder/demultiplexer with latches on the three address inputs. This device essentially combines the function and speed of the 'S138 1-of-8 decoder with a 3-bit storage latch. When the latch is enabled ( $\overline{LE} = LOW$ ), the 'S137 acts as a 1-of-8 active LOW decoder. When the Latch Enable ( $\overline{LE}$ ) goes from LOW to HIGH, the last data present at the inputs before this transition is stored in the latches. Further address changes are ignored as long as  $\overline{LE}$  remains HIGH. The output enable gate ( $\overline{E}_1 \bullet E_2$ ) controls the state of the outputs independent of the Address inputs or latch operation. All outputs are HIGH unless  $\overline{E}_1$  is LOW and  $E_2$  is HIGH. The 'S137 is ideally suited for implementing non-overlapping decoders in 3-state systems and strobed (stored address) applications in bus oriented systems. The 'S137 is fabricated with the Schottky barrier diode process for high speed.

- SCHOTTKY PROCESS FOR HIGH SPEED

- COMBINES 1-OF-8 DECODER WITH 3-BIT LATCH

- MULTIPLE INPUT ENABLE FOR EASY EXPANSION OR INDEPENDENT CONTROLS

- ACTIVE LOW MUTUALLY EXCLUSIVE OUTPUTS

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                         | MILITARY GRADE                                                                              | PKG  |

|--------------------|-----|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|

| PKGS               | OUT | $V_{CC} = +5.0 \text{ V } \pm 5\%,$<br>$T_A = 0^{\circ}\text{C to } +70^{\circ}\text{C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C}$ | TYPE |

| Plastic<br>DIP (P) | Α   | 74S137PC                                                                                 |                                                                                             | 9B   |

| Ceramic<br>DIP (D) | A   | 74S137DC                                                                                 | 54S137DM                                                                                    | 6B   |

| Flatpak<br>(F)     | A   | 74S137FC                                                                                 | 54S137FM                                                                                    | 4L   |

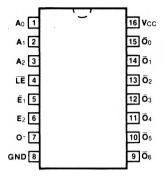

# CONNECTION DIAGRAM PINOUT A

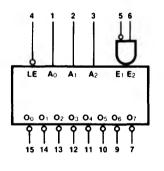

#### LOGIC SYMBOL

Vcc = Pin 16 GND = Pin 8

#### INPUT LOADING/FAN-OUT; See Section 3 for U.L. definitions

| PIN NAMES                         | DESCRIPTION                     | <b>54/74S (U.L.)</b><br>HIGH/LOW |

|-----------------------------------|---------------------------------|----------------------------------|

| A <sub>0</sub> — A <sub>2</sub>   | Address Inputs                  | 1.25/1.25                        |

| LE                                | Latch Enable Input (Active LOW) | 1.25/1.25                        |

| Ē <sub>1</sub>                    | Enable Input (Active LOW)       | 1.25/1.25                        |

| E <sub>2</sub>                    | Enable Input (Active HIGH)      | 1.25/1.25                        |

| $\overline{O}_0 - \overline{O}_7$ | Outputs (Active LOW)            | 25/12.5                          |

| ) I M |  |  |

|-------|--|--|

| INPUTS |        |                |                |                |                |   |    | OUT | PUT | s  |    |                |                |

|--------|--------|----------------|----------------|----------------|----------------|---|----|-----|-----|----|----|----------------|----------------|

| ΙĒ     | Ēı     | E <sub>2</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | ō | Ō1 | Ō2  | Ō₃  | Ō4 | Ō₅ | Ō <sub>6</sub> | Ō <sub>7</sub> |

| н      | нгнххх |                |                |                |                |   |    | ST. | ABL | Ξ  |    |                |                |

| х      | Н      | Х              | Х              | Х              | X              | н | Н  | Н   | Н   | Н  | Н  | Н              | Н              |

| X      | Х      | L              | Х              | X              | Χ              | н | Н  | Н   | Н   | Н  | Н  | Н              | Н              |

| L      | L      | н              | L              | L              | L              | L | н  | н   | н   | н  | н  | н              | н              |

| L      | L      | Н              | н              | L              | L              | н | L  | Н   | Н   | Н  | Н  | Н              | н              |

| L      | L      | Н              | L              | Н              | L              | Н | Н  | L   | Н   | Н  | Н  | Н              | н              |

| L      | L      | Н              | Н              | Н              | L              | H | Н  | Н   | L   | Н  | Н  | Н              | Н              |

| L      | L      | н              | L              | L              | н              | н | н  | н   | н   | L  | н  | н              | н              |

| L      | L      | н              | н              | L              | н              | н | Н  | Н   | Н   | Н  | L  | Н              | н              |

| L      | L      | Н              | L              | Н              | н              | Н | Н  | Н   | Н   | Н  | Н  | L              | н              |

| L      | L      | Н              | н              | Н              | н              | н | Н  | Н   | Н   | Н  | Н  | Н              | L              |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

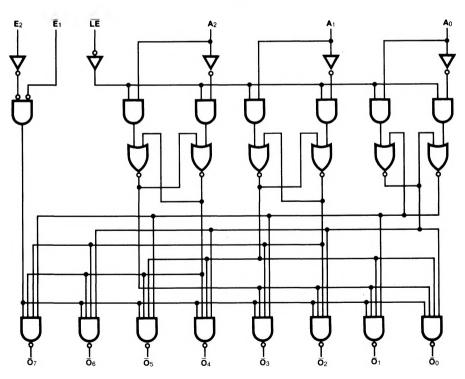

## LOGIC DIAGRAM

**FUNCTIONAL DESCRIPTION** — The 'S137.is a very high speed 1-of-8 decoder/demultiplexer fabricated with the Schottky barrier diode process. The decoder accepts three binary weighted inputs (A<sub>0</sub>, A<sub>1</sub>, A<sub>2</sub>) and when enabled provides eight mutually exclusive active LOW outputs ( $\overline{O}_0 - \overline{O}_7$ ). The 'S137 also features a 3-bit latch on the Address inputs. The device functions as a 1-of-8 decoder (same as 'S138) when the Latch Enable ( $\overline{LE}$ ) is LOW. When  $\overline{LE}$  is HIGH, the address present one setup time prior to the LOW-to-HIGH transition of  $\overline{LE}$  will be stored in the address latches and the outputs will not be affected by further address changes. The output enable control is an AND gate comprised of one active LOW input ( $\overline{E}_1$ ) and one active HIGH input ( $\overline{E}_2$ ). All outputs are HIGH unless the enable inputs ( $\overline{E}_1 \bullet E_2$ ) are in their true (active) state.

A non-overlapping decoder with edge-triggered address inputs can be easily implemented by tying the Latch Enable input  $\overline{LE}$  to the active HIGH Enable input (E2). When this input ( $\overline{LE} \bullet E_2$ ) is LOW, all outputs are forced HIGH and a new address enters the latches. When the  $\overline{LE} \bullet E_2$  input goes HIGH, the address is stored in the latches and the corresponding output gate is enabled (goes LOW). In this configuration, the address must be stable only one setup time prior to the LOW-to-HIGH transition of the  $\overline{LE} \bullet E_2$  input. The addressed output remains active LOW as long as the ( $\overline{LE} \bullet E_2$ ) input remains HIGH, even if the address changes. Data or control information can thus be strobed into the 'S137 from very noisy or bus oriented systems using a LOW pulse width equal to the minimum latch enable pulse width  $t_w(L)$ .

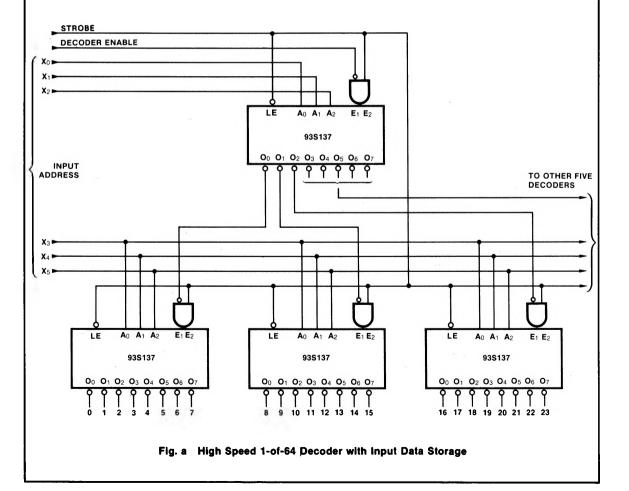

The multiple enable inputs along with the address latches allows easy expansion to a 1-of-64 decoder with nonoverlapping outputs (see *Figure* a).

| DC CHARACTERISTICS OVER OPERATING TEMPER | RATURE RANGE (unless otherwise specified) |

|------------------------------------------|-------------------------------------------|

|------------------------------------------|-------------------------------------------|

| SYMBOL | PARAMETER            | 54/ | 748 | UNITS | CONDITIONS            |  |

|--------|----------------------|-----|-----|-------|-----------------------|--|

|        |                      | Min | Max |       |                       |  |

| Icc    | Power Supply Current |     | 95  | mA    | V <sub>CC</sub> = Max |  |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C (See Section 3 for waveforms and load configurations)

|              |                                                       | 54/74\$  C <sub>L</sub> = 15 pF  R <sub>L</sub> = 280 Ω |          |    |                 |     |  |

|--------------|-------------------------------------------------------|---------------------------------------------------------|----------|----|-----------------|-----|--|

| SYMBOL       | PARAMETER                                             |                                                         |          |    |                 | - , |  |

|              |                                                       | Min                                                     | Max      | 1  |                 |     |  |

| tpLH<br>tpHL | Propagation Delay<br>A <sub>n</sub> to Ō <sub>n</sub> |                                                         | 12<br>20 | ns | Figs. 3-1, 3-20 |     |  |

| tpLH<br>tpHL | Propagation Delay<br>E <sub>1</sub> to O <sub>n</sub> |                                                         | 10<br>12 | ns | Figs. 3-1, 3-5  |     |  |

| tPLH<br>tPHL | Propagation Delay<br>E <sub>2</sub> to On             |                                                         | 12<br>12 | ns | Figs. 3-1, 3-4  |     |  |

| tPLH<br>tPHL | Propagation Delay<br>LE to On                         |                                                         | 12<br>20 | ns | Figs. 3-1, 3-9  |     |  |

## AC OPERATING REQUIREMENTS: VCC = +5.0 V, TA = +25°C

| SYMBOL             | PARAMETER                | 54/ | 745 | UNITS | CONDITIONS |  |

|--------------------|--------------------------|-----|-----|-------|------------|--|

|                    | - A.I.A.III-1-III        | Min | Max | ]     |            |  |

| t <sub>s</sub> (H) | Setup Time HIGH An to LE | 4.5 |     | ns    | Fig. 3-13  |  |

| th (H)             | Hold Time HIGH An to LE  | 0   |     | ns    |            |  |

| t <sub>s</sub> (L) | Setup Time LOW An to LE  | 6.5 |     | ns    | Fig. 3-13  |  |

| th (L)             | Hold Time LOW An to LE   | 0   |     | ns    | 1 1g. 0 10 |  |

| t <sub>w</sub> (L) | LE Pulse Width LOW       | 7.0 |     | ns    | Fig. 3-21  |  |