www.ti.com SLAS628-MARCH 2009

# 18-BIT, 1-MSPS, PSEUDO-BIPOLAR DIFFERENTIAL SAR ADC WITH ON-CHIP ADC DRIVER (OPA) AND 4-CHANNEL DIFFERENTIAL MULTIPLEXER

#### **FEATURES**

- 1.0-MHz Sample Rate, Zero Latency at Full Speed

- 18-Bit Resolution

- Supports Pseudo-Bipolar Differential Input Range: -4 V to +4 V with 2-V Common-Mode

- Built-In Four Channel, Differential Ended Multiplexer; with Channel Count Selection and Auto/Manual Mode

- On-Board Differential ADC Driver (OPA)

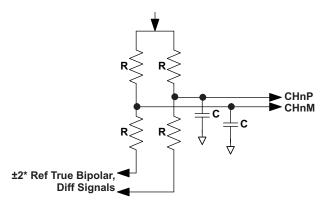

- Buffered Reference Output to Level Shift Bipolar ±4-V Input with External Resistance Divider

- Reference/2 Output to Set Common-Mode for External Signal Conditioner

- 18-/16-/8-Bit Parallel Interface

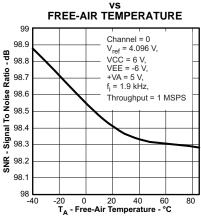

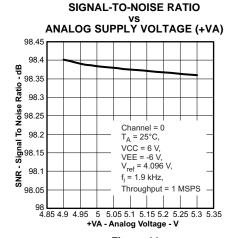

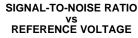

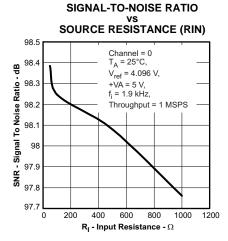

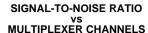

- SNR: 98.4dB Typ at 2-kHz I/P

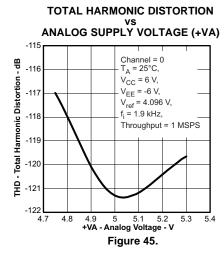

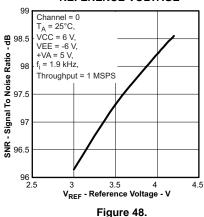

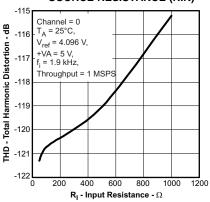

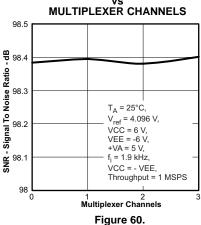

- THD: -119dB Typ at 2-kHz I/P

- Power Dissipation: 331.25 mW at 1 MSPS Including ADC Driver

- Internal Reference

- Internal Reference Buffer

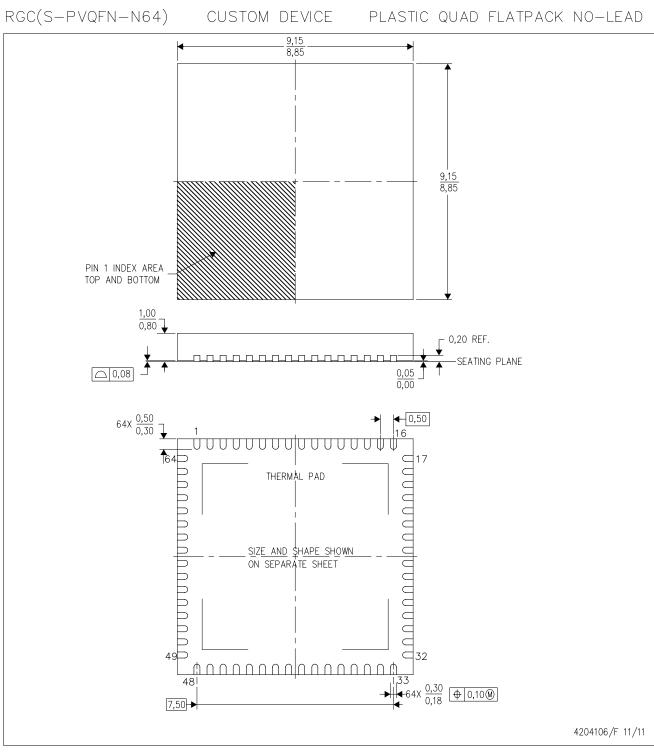

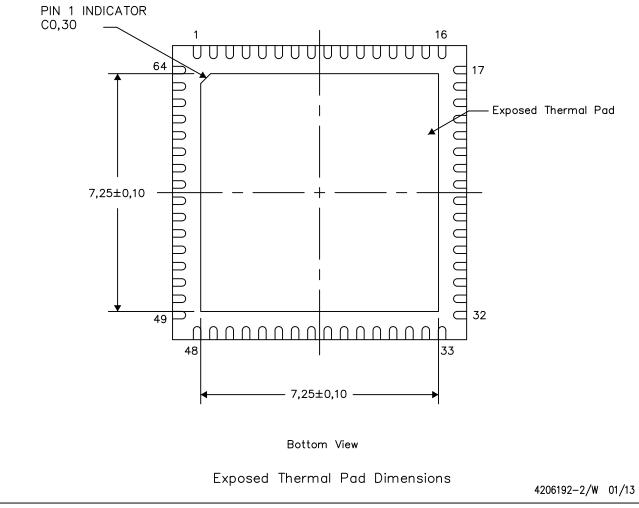

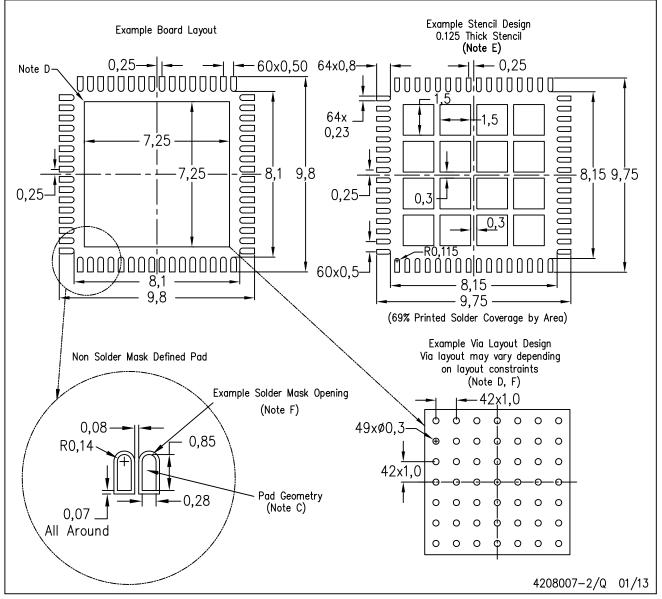

- 64-Pin QFN Package

#### **APPLICATIONS**

- Medical Imaging/CT Scanners

- Automated Test Equipment

- High-Speed Data Acquisition Systems

- High-Speed Closed-Loop Systems

#### DESCRIPTION

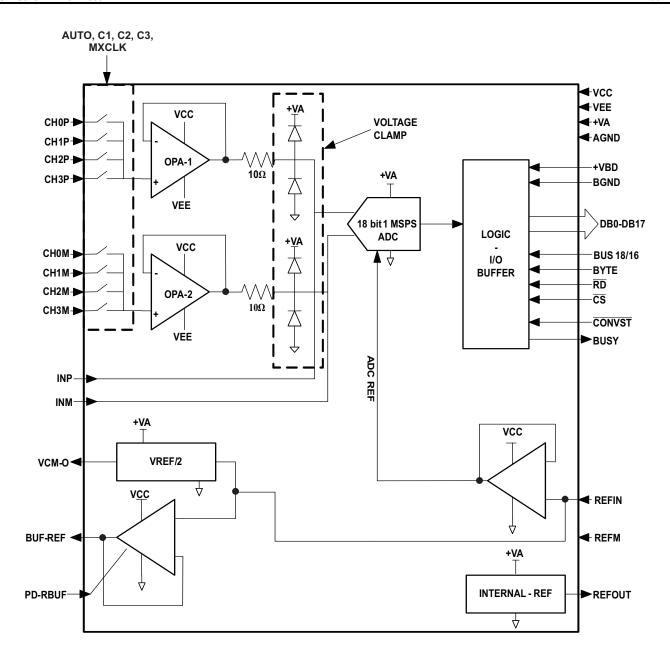

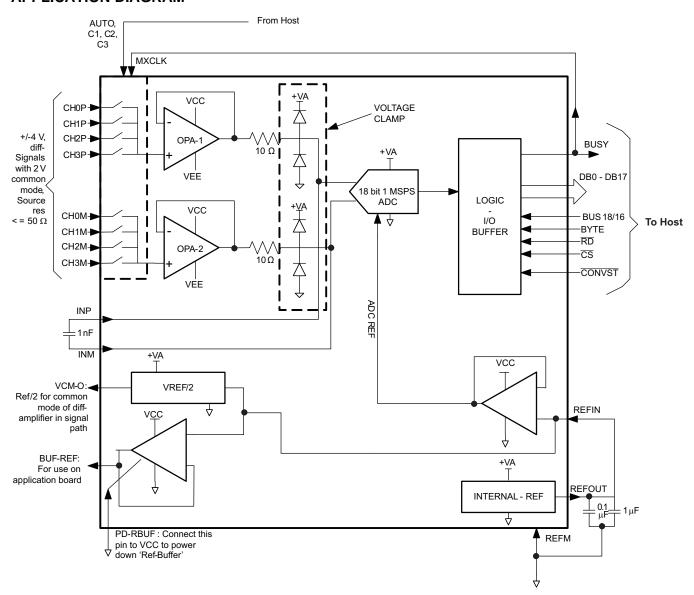

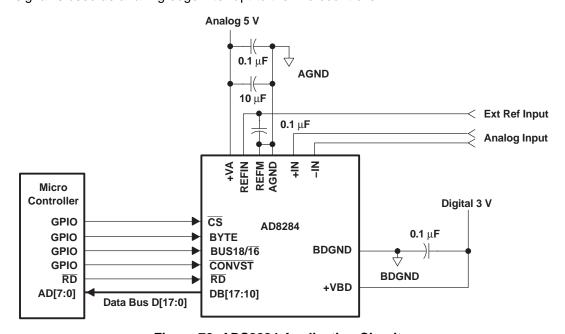

The ADS8284 is a high-performance analog system-on-chip (SoC) device with an 18-bit, 1-MSPS A/D converter, 4-V internal reference, an on-chip ADC driver (OPA), and a 4-channel differential multiplexer. The channel count of the multiplexer and auto/manual scan modes of the device are user selectable.

ADS8284

The ADC driver is designed to leverage the very high noise performance of the differential ADC at optimum power usage levels.

The ADS8284 outputs a buffered reference signal for level shifting of a  $\pm 4$ -V bipolar signal with an external resistance divider. A  $V_{ref}/2$  output signal is available to set the common-mode of a signal conditioning circuit. The device also includes an 18-/16-/8-bit parallel interface.

The ADS8284 is available in a 9 mm x 9 mm, 64-pin QFN package and is characterized from -40°C to 85°C.

#### HIGH-SPEED SAR CONVERTER FAMILY

| TYPE/SPEED                        | 500 kHz | ~600 kHz    | 750 kHz | 1 MHz   | 1.25 MHz    | 2 MHz       | 3 MHz   | 4MHz    |

|-----------------------------------|---------|-------------|---------|---------|-------------|-------------|---------|---------|

| 18-Bit Pseudo-Diff                | ADS8383 | ADS8381     |         | ADS8481 |             |             |         |         |

| To-Bit FSeudo-Dill                |         | ADS8380 (s) |         |         |             |             |         |         |

| 18-Bit Pseudo-Bipolar, Fully Diff |         | ADS8382 (s) |         | ADS8284 | ADS8484     |             |         |         |

| 16-Bit Pseudo-Bipolar, Fully Dill |         |             |         | ADS8482 |             |             |         |         |

|                                   | ADS8327 | ADS8370 (s) | ADS8371 | ADS8471 | ADS8401     | ADS8411     |         |         |

| 16-Bit Pseudo-Diff                | ADS8328 |             |         |         | ADS8405     | ADS8410 (s) |         |         |

|                                   | ADS8319 |             |         |         |             |             |         |         |

| 16-Bit Pseudo-Bipolar, Fully Diff | ADS8318 | ADS8372 (s) |         | ADS8472 | ADS8402     | ADS8412     |         | ADS8422 |

| то-ык Fseudo-ырогаг, Fully Dill   |         |             |         | ADS8254 | ADS8406     | ADS8413 (s) |         |         |

| 14-Bit Pseudo-Diff                |         |             |         |         | ADS7890 (s) |             | ADS7891 |         |

| 12-Bit Pseudo-Diff                |         |             |         | ADS7886 |             | ADS7883     |         | ADS7881 |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### ORDERING INFORMATION<sup>(1)</sup>

| MODEL     | MAXIMUM<br>INTEGRAL<br>LINEARITY<br>(LSB) | MAXIMUM<br>DIFFERENTIAL<br>LINEARITY<br>(LSB) | NO MISSING<br>CODES AT<br>RESOLUTION<br>(BIT) | PACKAGE<br>TYPE | PACKAGE<br>DESIGNATOR | TEMPERATURE<br>RANGE | ORDERING<br>INFORMATION | TRANSPORT<br>MEDIA<br>QUANTITY |    |    |    |    |    |    |    |            |     |          |               |

|-----------|-------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------|-----------------------|----------------------|-------------------------|--------------------------------|----|----|----|----|----|----|----|------------|-----|----------|---------------|

| ADS8284IB | ±2.5                                      | +1.5/–1                                       |                                               |                 |                       |                      | ADS8284IBRGCT           | 250                            |    |    |    |    |    |    |    |            |     |          |               |

| AD36264IB | ±2.5                                      | +1.5/-1                                       |                                               |                 | 10                    | 10                   | 10                      | 10                             | 10 | 10 | 10 | 10 | 10 | 10 | 10 | 64-pin QFN | RGC | −40°C to | ADS8284IBRGCR |

| ADS8284I  | ±4.5                                      | +1.5/–1                                       |                                               | 04-piii QFN     | RGC                   | 85°C                 | ADS8284IRGCT            | 250                            |    |    |    |    |    |    |    |            |     |          |               |

| AD362641  | ±4.5                                      | +1.5/-1                                       | 18                                            |                 |                       |                      | ADS8284IRGCR            | 2000                           |    |    |    |    |    |    |    |            |     |          |               |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

#### **ABSOLUTE MAXIMUM RATINGS**(1)

over operating free-air temperature range (unless otherwise noted)

|                                           | ·                     | VALUE                                     | UNIT |

|-------------------------------------------|-----------------------|-------------------------------------------|------|

| CH(i) to AGND (both P and M i             | nputs)                | VEE-0.3 to VCC + 0.3                      | V    |

| VCC to VEE                                |                       | -0.3 to 18                                | V    |

| +VA to AGND                               |                       | -0.3 to 7                                 | V    |

| +VBD to BDGND                             |                       | -0.3 to 7                                 | V    |

| ADC control digital input voltag          | e to GND              | -0.3 to (+VBD + 0.3)                      | V    |

| ADC control digital output to G           | ND                    | -0.3 to (+VBD + 0.3)                      | V    |

| Multiplexer control digital input         | voltage to GND        | -0.3 to (+VA + 0.3)                       | V    |

| Power control digital input volta         | ge to GND             | -0.3 to (+VCC + 0.3)                      | V    |

| Operating temperature range               |                       | -40 to 85                                 | °C   |

| Storage temperature range                 |                       | -65 to 150                                | °C   |

| Junction temperature (T <sub>J</sub> max) |                       | 150                                       | °C   |

| OFN poekees                               | Power dissipation     | (T <sub>J</sub> Max–T <sub>A</sub> )/ θJA |      |

| QFN package                               | θJA Thermal impedance | 86                                        | °C/W |

| l   t t                                   | Vapor phase (60 sec)  | 215                                       | °C   |

| Lead temperature, soldering               | Infrared (15 sec)     | 220                                       | °C   |

|                                           |                       |                                           |      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

SLAS628-MARCH 2009 www.ti.com

#### **SPECIFICATIONS**

$T_A = -40$  °C to 85 °C, VCC = 5 V, VEE = -5 V, +VA = 5 V, +VBD = 5 V or 3.3 V,  $V_{ref} = 4$  V,  $f_{SAMPLE} = 1$  MSPS (unless otherwise noted)

| PARA                                           | METER                            | TEST CONDITIONS                                                                           | MIN                            | TYP                   | MAX                            | UNIT               |  |

|------------------------------------------------|----------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|-----------------------|--------------------------------|--------------------|--|

| ANALOG INPUT                                   |                                  |                                                                                           |                                |                       |                                |                    |  |

| Full-scale input voltage at m                  | nultiplexer input <sup>(1)</sup> | CH(i)P-CH(i)M                                                                             | -V <sub>ref</sub>              |                       | $V_{ref}$                      | V                  |  |

| Absolute input range at mul                    | tiplexer input                   | CH (i)                                                                                    | -0.2                           |                       | $V_{ref}$ + 0.2                | V                  |  |

| Input common-mode voltage                      | е                                | [CH(i)P + CH(i)M] /2                                                                      | (V <sub>ref</sub> )/2<br>- 0.2 | (V <sub>ref</sub> )/2 | (V <sub>ref</sub> )/2<br>+ 0.2 | V                  |  |

| SYSTEM PERFORMANCE                             |                                  |                                                                                           |                                |                       |                                |                    |  |

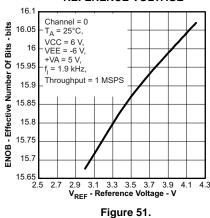

| Resolution                                     |                                  |                                                                                           |                                | 18                    |                                | Bits               |  |

|                                                | ADS8284IB                        |                                                                                           | 18                             |                       |                                |                    |  |

| No missing codes                               | ADS8284I                         |                                                                                           | 18                             |                       |                                | Bits               |  |

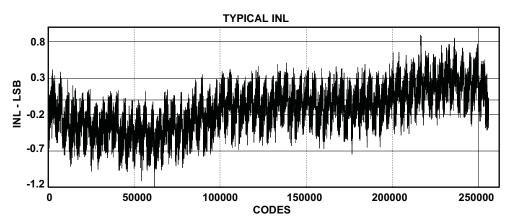

|                                                | ADS8284IB                        |                                                                                           | -2.5                           | ±1.25                 | 2.5                            | (=)                |  |

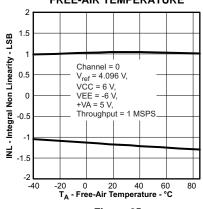

| Integral linearity (2)                         | ADS8284I                         |                                                                                           | -4.5                           | ±1.5                  | 4.5                            | LSB (3)            |  |

|                                                | ADS8284IB                        |                                                                                           | -1                             | ±0.6                  | 1.5                            |                    |  |

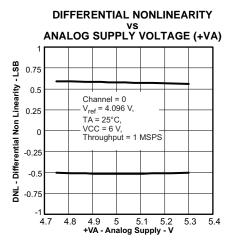

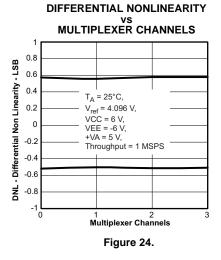

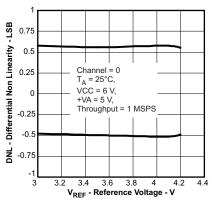

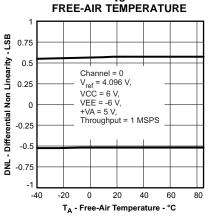

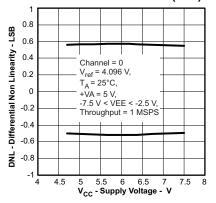

| Differential linearity                         | ADS8284I                         | At 18-bit level                                                                           | -1                             | ±0.6                  | 1.5                            | LSB <sup>(3)</sup> |  |

|                                                | ADS8284IB                        |                                                                                           | -0.5                           | ±0.05                 | 0.5                            |                    |  |

| Offset error                                   | ADS8284I                         |                                                                                           | -0.5                           | ±0.05                 | 0.5                            | mV                 |  |

|                                                | ADS8284IB                        |                                                                                           | -0.1                           | ±0.025                | 0.1                            |                    |  |

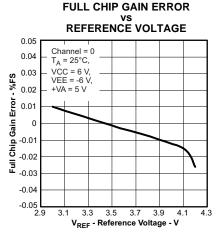

| Gain error <sup>(4)</sup>                      | ADS8284I                         | External reference                                                                        | -0.1                           | ±0.025                | 0.1                            | %FS                |  |

| DC power supply rejection ratio                |                                  | At 3FFF0 <sub>H</sub> output code. For +VA or VCC, VEE variation of 0.5 V individually    | -0.1                           | 80                    | 0.1                            | dB                 |  |

| SAMPLING DYNAMICS                              |                                  |                                                                                           |                                |                       |                                |                    |  |

|                                                |                                  | +VBD = 5 V                                                                                |                                | 625                   | 650                            | ns                 |  |

| Conversion time                                |                                  | +VDB = 3 V                                                                                |                                | 625                   | 650                            | ns                 |  |

|                                                |                                  | +VBD = 5 V                                                                                | 320                            | 350                   |                                | ns                 |  |

| Acquisition time                               |                                  | +VDB = 3 V                                                                                | 320                            | 350                   |                                |                    |  |

| Maximum throughput rate                        |                                  |                                                                                           | 020                            |                       | 1.0                            | MHz                |  |

| Aperture delay                                 |                                  |                                                                                           |                                | 4                     | -                              | ns                 |  |

| Aperture jitter                                |                                  |                                                                                           |                                | 5                     |                                | ps                 |  |

| · + - · · · · · · · · · · · · · · · · ·        |                                  | For ADC only                                                                              |                                | 150                   |                                | ns                 |  |

| Settling time to 0.5 LSB                       |                                  | For OPA (OP1, OP2) + mux                                                                  |                                | 700                   |                                |                    |  |

| Over voltage recovery                          |                                  | For ADC only                                                                              |                                | 150                   |                                | ns                 |  |

| DYNAMIC CHARACTERIS                            | TICS                             | 1. 5. 1. 2. 5 1. 1.                                                                       |                                |                       |                                |                    |  |

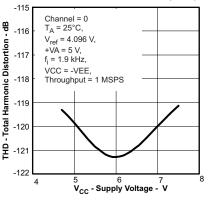

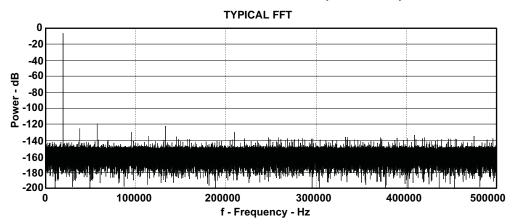

|                                                | ADS8284I                         |                                                                                           |                                | -119                  |                                |                    |  |

|                                                | ADS8284IB                        | $V_{IN} = 4 V_{pp}$ at 2 kHz                                                              |                                | -119                  |                                | dB                 |  |

| Tatal bassassia distantias                     | ADS8284I                         |                                                                                           |                                | -105                  |                                |                    |  |

| Total harmonic distortion (THD) <sup>(5)</sup> | ADS8284IB                        | $V_{IN} = 4 V_{pp}$ at 10 kHz                                                             |                                | -105                  |                                | dB                 |  |

|                                                | ADS8284I                         | V 4 V 4 400 LLL                                                                           |                                | -100                  |                                |                    |  |

|                                                | ADS8284IB                        | $V_{\text{IN}} = 4 \text{ V}_{\text{pp}} \text{ at } 100 \text{ kHz},$ $\text{LoPWR} = 0$ |                                | -100                  |                                | dB                 |  |

|                                                | ADS8284I                         |                                                                                           |                                | 98.4                  |                                |                    |  |

|                                                | ADS8284IB                        | $V_{IN} = 4 V_{pp}$ at 2 kHz                                                              | 97.5                           | 98.4                  |                                |                    |  |

|                                                | ADS8284IB                        |                                                                                           | 98                             |                       |                                |                    |  |

| Signal-to-noise ratio (SNR)                    |                                  | $V_{IN} = 4 V_{pp}$ at 10 kHz                                                             |                                |                       | dB                             |                    |  |

|                                                | ADS8284IB                        |                                                                                           |                                | 98                    |                                |                    |  |

|                                                | ADS8284I                         | $V_{IN} = 4 V_{pp}$ at 100 kHz,<br>LoPWR = 0                                              |                                | 95                    |                                | dB                 |  |

|                                                | ADS8284IB                        | LOI WIX = 0                                                                               |                                | 97                    |                                |                    |  |

<sup>(1)</sup> Ideal input span, does not include gain or offset error.

<sup>(2)</sup> This is endpoint INL, not best fit.

<sup>(3)</sup> LSB means least significant bit.

<sup>(4)</sup> Calculated on the first nine harmonics of the input frequency.

<sup>(5)</sup> Measured relative to acutal measured reference.

#### **SPECIFICATIONS** (continued)

$T_A = -40$ °C to 85°C, VCC = 5 V, VEE = -5 V, +VA = 5 V, +VBD = 5 V or 3.3 V,  $V_{ref} = 4$  V,  $f_{SAMPLE} = 1$  MSPS (unless otherwise noted)

| PARAI                                   | METER                                   | TEST CONDITIONS                                                                           | MIN                   | TYP      | MAX                    | UNIT     |

|-----------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------|-----------------------|----------|------------------------|----------|

|                                         | ADS8284I                                | V 4 V ot 2 ld la                                                                          |                       | 98.3     |                        | 40       |

|                                         | ADS8284IB                               | $V_{IN} = 4 V_{pp}$ at 2 kHz                                                              |                       | 98.3     |                        | dB       |

| Signal-to-noise + distortion            | ADS8284I                                | V = 4 V ot 10 kHz                                                                         |                       | 97.2     |                        | ٩D       |

| (SINAD)                                 | ADS8284IB                               | $V_{IN} = 4 V_{pp}$ at 10 kHz                                                             |                       | 97.2     |                        | dB       |

|                                         | ADS8284I                                | $V_{IN} = 4 V_{DD}$ at 100 kHz,                                                           |                       | 93.8     |                        | 70       |

|                                         | ADS8284IB                               | $V_{\text{IN}} = 4 \text{ V}_{\text{pp}} \text{ at } 100 \text{ kHz},$ $\text{LoPWR} = 0$ |                       | 95.23    |                        | dB       |

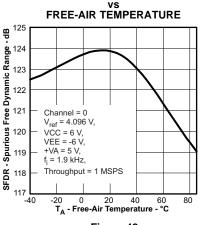

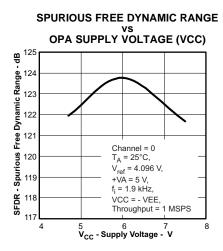

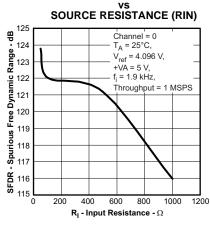

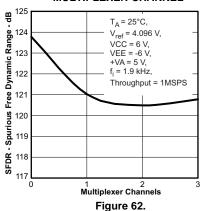

|                                         | ADS8284I                                | V 4V 40111                                                                                |                       | 121      |                        | ī        |

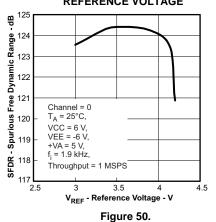

|                                         | ADS8284IB                               | $V_{IN} = 4 V_{pp}$ at 2 kHz                                                              |                       | 121      |                        | dB       |

| Spurious free dynamic                   | ADS8284I                                | N 4N 4011                                                                                 |                       | 106      |                        |          |

| range (SFDR)                            | ADS8284IB                               | $V_{IN} = 4 V_{pp}$ at 10 kHz                                                             |                       | 106      |                        | dB       |

|                                         | ADS8284I                                | $V_{IN} = 4 V_{co}$ at 100 kHz.                                                           |                       | 101      |                        |          |

|                                         | ADS8284IB                               | $V_{IN} = 4 V_{pp}$ at 100 kHz,<br>LoPWR = 0                                              |                       | 101      |                        | dB       |

| -3dB small signal bandwidth             | 1                                       |                                                                                           |                       | 8        |                        | MHz      |

| VOLTAGE REFERENCE IN                    | IPUT (REFIN)                            |                                                                                           |                       |          |                        | 1        |

| Reference voltage at REFIN              |                                         |                                                                                           | 3.0                   | 4.096    | +VA - 0.8              | V        |

| Reference input current <sup>(6)</sup>  |                                         |                                                                                           |                       | 1        | 1                      | μА       |

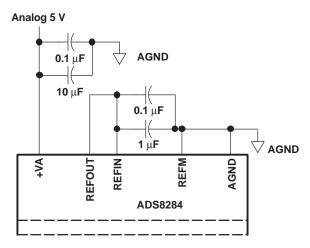

| INTERNAL REFERENCE C                    | UTPUT (REFOUT)                          |                                                                                           |                       |          |                        | •        |

| Internal reference start-up ti          | • • • • • • • • • • • • • • • • • • • • | From 95% (+VA), with 1-μF storage capacitor                                               |                       |          | 120                    | ms       |

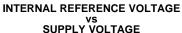

| Reference voltage range, V <sub>r</sub> |                                         | , , , , , , , , , , , , , , , , , , , ,                                                   | 4.081                 | 4.096    | 4.111                  | V        |

| Source current                          | 61                                      | Static load                                                                               |                       |          | 10                     | μА       |

| Line regulation                         |                                         | +VA = 4.75 V to 5.25 V                                                                    |                       |          | μV                     |          |

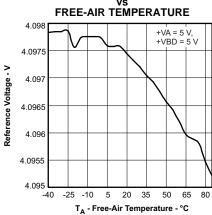

| Drift                                   |                                         | I <sub>O</sub> = 0                                                                        |                       | 60<br>±6 |                        | PPM/°C   |

| BUFFERED REFERENCE                      | OUTPUT (BUF-REF)                        | 1.0 5                                                                                     |                       |          |                        |          |

| Output current                          |                                         | REFIN = 4 V, at 85°C                                                                      |                       | 70       |                        | mA       |

| REFERENCE/2 OUTPUT (\                   | (CMO)                                   | 112 17, 4. 55 5                                                                           |                       |          |                        |          |

| Output current                          |                                         | REFIN = 4 V, at +85°C                                                                     |                       | 50       |                        | μА       |

| ANALOG MULTIPLEXER                      |                                         |                                                                                           |                       |          |                        | <b>P</b> |

| Number of channels                      |                                         |                                                                                           |                       |          | 4                      |          |

| Channel to channel crosstal             | k                                       | 100 kHz i/p                                                                               |                       | -95      | <u>'</u>               | dB       |

| Channel selection                       |                                         | Auto sequencer with selection of channel count or manual selection through control lines  |                       |          |                        | <u> </u> |

| DIGITAL INPUT-OUTPUT                    |                                         |                                                                                           |                       |          |                        | <u> </u> |

| ADC CONTROL PINS                        |                                         |                                                                                           |                       |          |                        |          |

| Logic Family-CMOS                       |                                         |                                                                                           |                       |          |                        |          |

|                                         | V <sub>IH</sub>                         | I <sub>IH</sub> = 5 μA                                                                    | +V <sub>BD</sub> -1   |          | +V <sub>BD</sub> + 0.3 | V        |

|                                         | V <sub>IL</sub>                         | $I_{IL} = 5 \mu A$                                                                        | 0.3                   |          | 0.8                    | V        |

| Logic level                             | V <sub>OH</sub>                         | I <sub>OH</sub> = 2 TTL loads                                                             | +V <sub>BD</sub> -0.6 |          | +V <sub>BD</sub>       | V        |

|                                         | V <sub>OL</sub>                         | I <sub>OL</sub> = 2 TTL loads                                                             | 0                     |          | 0.4                    | V        |

| MULTIPLEXER CONTROL                     |                                         | -OL - 2 1 12 10000                                                                        |                       |          | 0.4                    | · •      |

| Logic Family - CMOS                     |                                         |                                                                                           |                       |          |                        |          |

| Logic Fairing * Olvico                  | I                                       | I <sub>IH</sub> = 5 μA                                                                    | 2.3                   |          | +VA +0.3               | V        |

| Logic level                             | I <sub>IH</sub>                         | $I_{IL} = 5 \mu A$                                                                        | -0.3                  |          | 0.8                    | V        |

| POWER CONTROL PINS                      | I <sub>IL</sub>                         | 1 L − 0 μΛ                                                                                | -0.3                  |          | 0.0                    | V        |

| Logic Family - CMOS                     |                                         |                                                                                           |                       |          |                        |          |

| Logic I allilly - CIVIOS                | V                                       | I <sub>IH</sub> = 5 μA                                                                    | 2.3                   |          | +VA +0.3               | V        |

|                                         |                                         | 1 m = 3 HA                                                                                | / .3                  |          | ナッハ ナリ.づ               | V        |

| Logic level                             | V <sub>IH</sub>                         | $I_{IL} = 5 \mu\text{A}$                                                                  | -0.3                  |          | 0.8                    | V        |

(6) Can vary ±20%

#### **SPECIFICATIONS** (continued)

$T_A = -40$ °C to 85°C, VCC = 5 V, VEE = -5 V, +VA = 5 V, +VBD = 5 V or 3.3 V,  $V_{ref} = 4$  V,  $f_{SAMPLE} = 1$  MSPS (unless otherwise noted)

| PARAI                                         | METER                       | TEST CONDITIONS                                                                         | MIN  | TYP   | MAX  | UNIT |

|-----------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------|------|-------|------|------|

|                                               | +VBD                        |                                                                                         | 2.7  | 3.3   | 5.25 | V    |

| Dower aupply voltage                          | +VA                         |                                                                                         | 4.75 | 5     | 5.25 | V    |

| Power supply voltage                          | VCC                         |                                                                                         | 4.75 | 5     | 7.5  | V    |

|                                               | VEE                         |                                                                                         | -7.5 | -5    | -3   | V    |

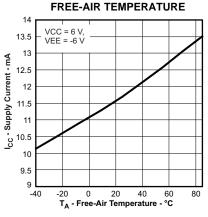

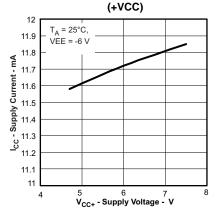

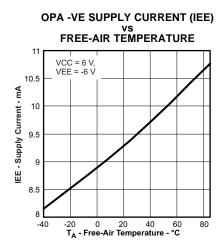

| ADC driver positive supply (<br>OP2 together) | VCC) current (for OP1 and   | VCC = +5, VEE = -5V, CH0 - CH3 p and m inputs shorted to each other and connected to 2V |      | 11.65 |      | mA   |

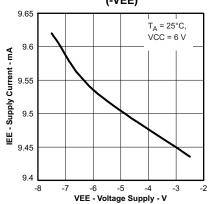

| ADC driver negative supply OP1 together)      | ( VEE) current (for OP1 and | VCC= +5V, CH0 - CH3 p and m inputs shorted to each other and connected to 2V            |      | 9.6   |      | mA   |

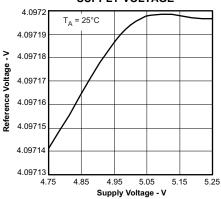

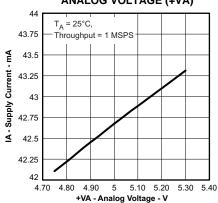

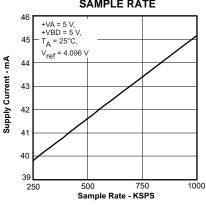

| +VA supply current, 1-MHz                     | sample rate                 |                                                                                         |      | 45    | 50   | mA   |

| Reference buffer (BUF-REF                     | ) supply current (VCC to    | VCC= +5, PD-RBUF = 0, Quiescent current                                                 |      | 8     |      | mA   |

| GND)                                          |                             | VCC = 5, PD-RBUF = 1 <sup>(7)</sup>                                                     |      | 10    |      | μΑ   |

| TEMPERATURE RANGE                             |                             |                                                                                         |      |       | ,    |      |

| Operating free-air                            |                             |                                                                                         | -40  |       | 85   | °C   |

<sup>(7)</sup> PD-RBUF = 1 powers down the reference buffer (BUF-REF), note that it does not 3-state the BUF-REF output.

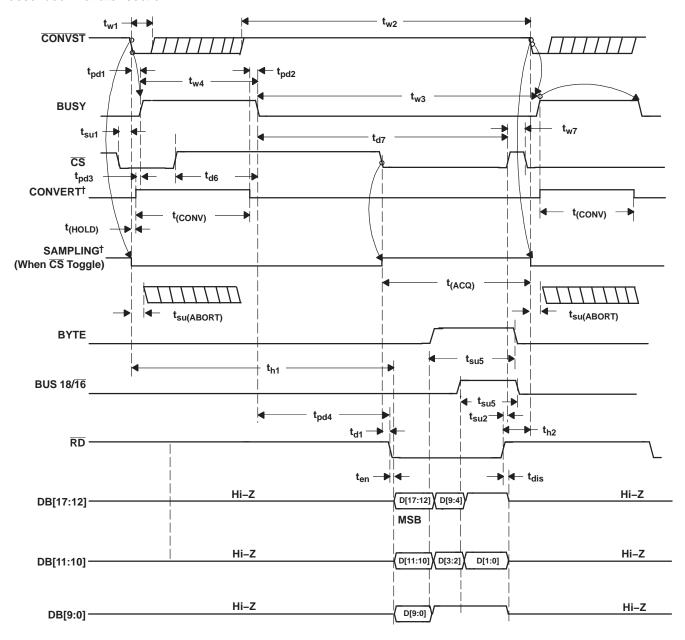

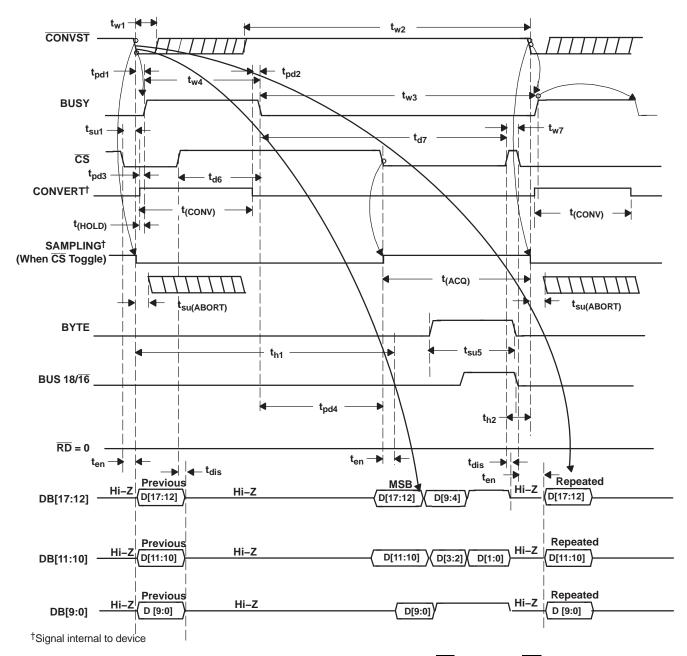

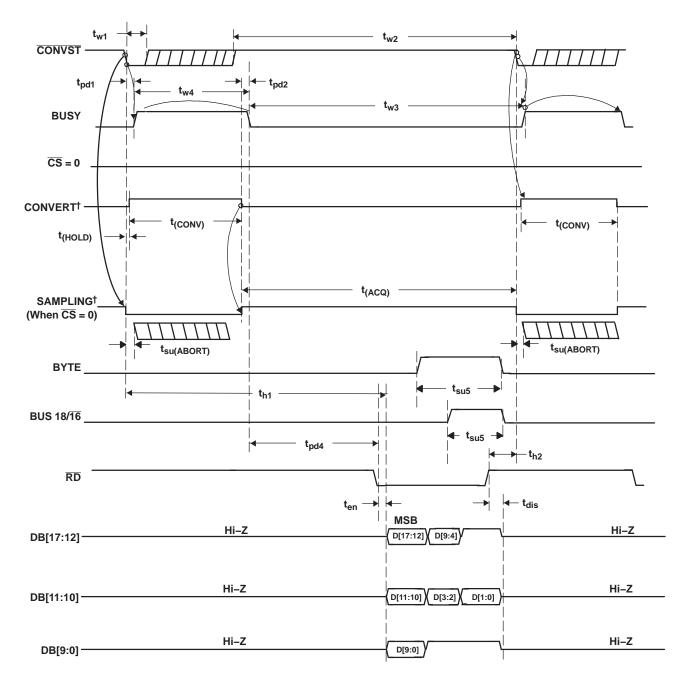

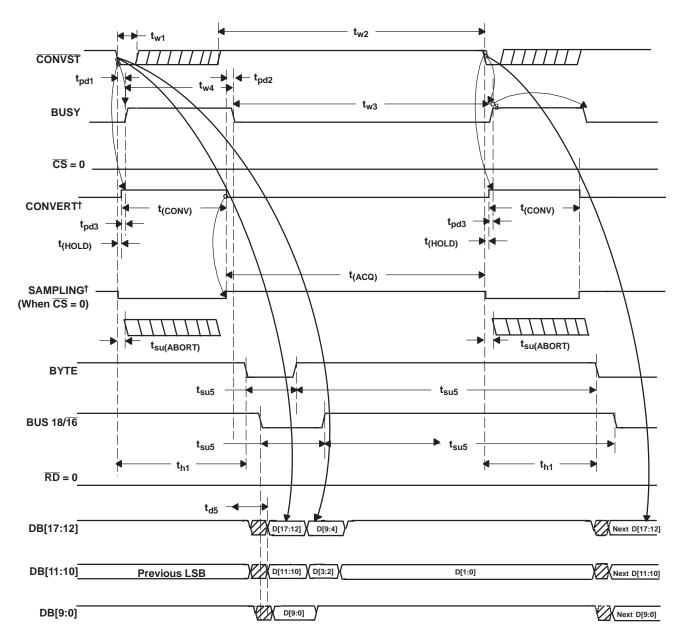

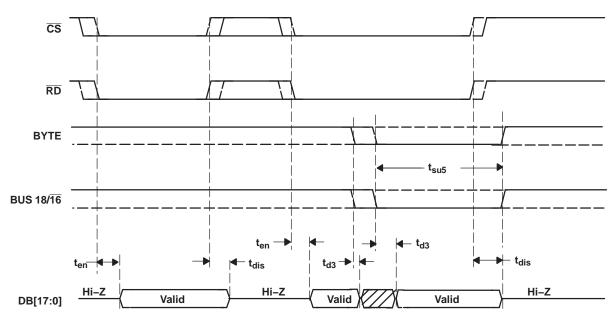

#### **TIMING REQUIREMENTS**

All specifications typical at  $-40^{\circ}$ C to  $85^{\circ}$ C, +VA = +VBD = 5 V (1) (2) (3)

|                        | PARAMETER                                                                                                                                                                                                                                                                                                        | MIN                    | TYP MAX | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|------|

| t <sub>(CONV)</sub>    | Conversion time                                                                                                                                                                                                                                                                                                  |                        | 650     | ns   |

| t <sub>(ACQ)</sub>     | Acquisition time                                                                                                                                                                                                                                                                                                 | 320                    |         | ns   |

| t <sub>(HOLD)</sub>    | Sample capacitor hold time                                                                                                                                                                                                                                                                                       |                        | 25      | ns   |

| t <sub>pd1</sub>       | CONVST low to BUSY high                                                                                                                                                                                                                                                                                          |                        | 40      | ns   |

| t <sub>pd2</sub>       | Propagation delay time, end of conversion to BUSY low                                                                                                                                                                                                                                                            |                        | 15      | ns   |

| t <sub>pd3</sub>       | Propagation delay time, start of convert state to rising edge of BUSY                                                                                                                                                                                                                                            |                        | 15      | ns   |

| t <sub>w1</sub>        | Pulse duration, CONVST low                                                                                                                                                                                                                                                                                       | 40                     |         | ns   |

| t <sub>su1</sub>       | Setup time, $\overline{\text{CS}}$ low to $\overline{\text{CONVST}}$ low                                                                                                                                                                                                                                         | 20                     |         | ns   |

| t <sub>w2</sub>        | Pulse duration, CONVST high                                                                                                                                                                                                                                                                                      | 20                     |         | ns   |

|                        | CONVST falling edge jitter                                                                                                                                                                                                                                                                                       |                        | 10      | ps   |

| t <sub>w3</sub>        | Pulse duration, BUSY signal low                                                                                                                                                                                                                                                                                  | t <sub>(ACQ)</sub> min |         | ns   |

| t <sub>w4</sub>        | Pulse duration, BUSY signal high                                                                                                                                                                                                                                                                                 |                        | 650     | ns   |

| t <sub>h1</sub>        | Hold time, first data bus transition (RD low, or CS low for read cycle, or BYTE or BUS18/16 input changes) after CONVST low                                                                                                                                                                                      | 40                     |         | ns   |

| t <sub>d1</sub>        | Delay time, $\overline{\text{CS}}$ low to $\overline{\text{RD}}$ low                                                                                                                                                                                                                                             | 0                      |         | ns   |

| t <sub>su2</sub>       | Setup time, $\overline{\text{RD}}$ high to $\overline{\text{CS}}$ high                                                                                                                                                                                                                                           | 0                      |         | ns   |

| t <sub>w5</sub>        | Pulse duration, RD low                                                                                                                                                                                                                                                                                           | 50                     |         | ns   |

| t <sub>en</sub>        | Enable time, RD low (or CS low for read cycle) to data valid                                                                                                                                                                                                                                                     |                        | 20      | ns   |

| t <sub>d2</sub>        | Delay time, data hold from RD high                                                                                                                                                                                                                                                                               | 5                      |         | ns   |

| t <sub>d3</sub>        | Delay time, BUS18/16 or BYTE rising edge or falling edge to data valid                                                                                                                                                                                                                                           | 10                     | 20      | ns   |

| t <sub>w6</sub>        | Pulse duration, RD high                                                                                                                                                                                                                                                                                          | 20                     |         | ns   |

| t <sub>w7</sub>        | Pulse duration, CS high                                                                                                                                                                                                                                                                                          | 20                     |         | ns   |

| t <sub>h2</sub>        | Hold time, last RD (or CS for read cycle ) rising edge to CONVST falling edge                                                                                                                                                                                                                                    | 50                     |         | ns   |

| t <sub>pd4</sub>       | Propagation delay time, BUSY falling edge to next $\overline{\text{RD}}$ (or $\overline{\text{CS}}$ for read cycle) falling edge                                                                                                                                                                                 | 0                      |         | ns   |

| t <sub>d4</sub>        | Delay time, BYTE edge to BUS18/16 edge skew                                                                                                                                                                                                                                                                      | 0                      |         | ns   |

| t <sub>su3</sub>       | Setup time, BYTE or BUS18/16 transition to RD falling edge                                                                                                                                                                                                                                                       | 10                     |         | ns   |

| t <sub>h3</sub>        | Hold time, BYTE or BUS18/16 transition to RD falling edge                                                                                                                                                                                                                                                        | 10                     |         | ns   |

| t <sub>dis</sub>       | Disable time, RD high (CS high for read cycle) to 3-stated data bus                                                                                                                                                                                                                                              |                        | 20      | ns   |

| t <sub>d5</sub>        | Delay time, BUSY low to MSB data valid delay                                                                                                                                                                                                                                                                     |                        | 0       | ns   |

| t <sub>d6</sub>        | Delay time, CS rising edge to BUSY falling edge                                                                                                                                                                                                                                                                  | 50                     |         | ns   |

| t <sub>d7</sub>        | Delay time, BUSY falling edge to CS rising edge                                                                                                                                                                                                                                                                  | 50                     |         | ns   |

| t <sub>su5</sub>       | BYTE transition setup time, from BYTE transition to next BYTE transition, or BUS18/16 transition setup time, from BUS18/16 to next BUS18/16.                                                                                                                                                                     | 50                     |         | ns   |

| t <sub>su(ABORT)</sub> | Setup time from the <u>falling edge</u> of $\overline{CONVST}$ (used to start the valid conversion) to the next falling edge of $\overline{CONVST}$ (when $\overline{CS}$ = 0 and $\overline{CONVST}$ are used to abort) or to the next falling edge of $\overline{CS}$ (when $\overline{CS}$ is used to abort). | 60                     | 550     | ns   |

<sup>(1)</sup> All input signals are specified with  $t_r = t_f = 5$  ns (10% to 90% of +VBD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . (2) See timing diagrams.

All timing are measured with 20 pF equivalent loads on all data bits and BUSY pins.

SLAS628-MARCH 2009 www.ti.com

## **INSTRUMENTS**

#### **TIMING REQUIREMENTS**

All specifications typical at -40°C to 85°C, +VA = 5 V +VBD = 3 V  $^{(1)}$   $^{(2)}$   $^{(3)}$

|                        | PARAMETER                                                                                                                                                                                                                                                                                      | MIN                    | TYP | MAX | UNIT |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|------|

| t <sub>(CONV)</sub>    | Conversion time                                                                                                                                                                                                                                                                                |                        |     | 650 | ns   |

| t <sub>(ACQ)</sub>     | Acquisition time                                                                                                                                                                                                                                                                               | 320                    |     |     | ns   |

| t <sub>(HOLD)</sub>    | Sample capacitor hold time                                                                                                                                                                                                                                                                     |                        |     | 25  | ns   |

| t <sub>pd1</sub>       | CONVST low to BUSY high                                                                                                                                                                                                                                                                        |                        |     | 40  | ns   |

| t <sub>pd2</sub>       | Propagation delay time, end of conversion to BUSY low                                                                                                                                                                                                                                          |                        |     | 25  | ns   |

| t <sub>pd3</sub>       | Propagation delay time, start of convert state to rising edge of BUSY                                                                                                                                                                                                                          |                        |     | 25  | ns   |

| t <sub>w1</sub>        | Pulse duration, CONVST low                                                                                                                                                                                                                                                                     | 40                     |     |     | ns   |

| t <sub>su1</sub>       | Setup time, $\overline{\text{CS}}$ low to $\overline{\text{CONVST}}$ low                                                                                                                                                                                                                       | 20                     |     |     | ns   |

| t <sub>w2</sub>        | Pulse duration, CONVST high                                                                                                                                                                                                                                                                    | 20                     |     |     | ns   |

|                        | CONVST falling edge jitter                                                                                                                                                                                                                                                                     |                        |     | 10  | ps   |

| t <sub>w3</sub>        | Pulse duration, BUSY signal low                                                                                                                                                                                                                                                                | t <sub>(ACQ)</sub> min |     |     | ns   |

| t <sub>w4</sub>        | Pulse duration, BUSY signal high                                                                                                                                                                                                                                                               |                        |     | 650 | ns   |

| t <sub>h1</sub>        | Hold time, first data bus transition (RD low, or CS low for read cycle, or BYTE or BUS18/16 input changes) after CONVST low                                                                                                                                                                    | 40                     |     |     | ns   |

| t <sub>d1</sub>        | Delay time, $\overline{\text{CS}}$ low to $\overline{\text{RD}}$ low                                                                                                                                                                                                                           | 0                      |     |     | ns   |

| t <sub>su2</sub>       | Setup time, $\overline{RD}$ high to $\overline{CS}$ high                                                                                                                                                                                                                                       | 0                      |     |     | ns   |

| t <sub>w5</sub>        | Pulse duration, RD low                                                                                                                                                                                                                                                                         | 50                     |     |     | ns   |

| t <sub>en</sub>        | Enable time, $\overline{\text{RD}}$ low (or $\overline{\text{CS}}$ low for read cycle) to data valid                                                                                                                                                                                           |                        |     | 30  | ns   |

| t <sub>d2</sub>        | Delay time, data hold from RD high                                                                                                                                                                                                                                                             | 5                      |     |     | ns   |

| t <sub>d3</sub>        | Delay time, BUS18/16 or BYTE rising edge or falling edge to data valid                                                                                                                                                                                                                         | 10                     |     | 30  | ns   |

| t <sub>w6</sub>        | Pulse duration, RD high                                                                                                                                                                                                                                                                        | 20                     |     |     | ns   |

| t <sub>w7</sub>        | Pulse duration, CS high                                                                                                                                                                                                                                                                        | 20                     |     |     | ns   |

| t <sub>h2</sub>        | Hold time, last RD (or CS for read cycle ) rising edge to CONVST falling edge                                                                                                                                                                                                                  | 50                     |     |     | ns   |

| t <sub>pd4</sub>       | Propagation delay time, BUSY falling edge to next $\overline{\text{RD}}$ (or $\overline{\text{CS}}$ for read cycle) falling edge                                                                                                                                                               | 0                      |     |     | ns   |

| t <sub>d4</sub>        | Delay time, BYTE edge to BUS18/16 edge skew                                                                                                                                                                                                                                                    | 0                      |     |     | ns   |

| t <sub>su3</sub>       | Setup time, BYTE or BUS18/16 transition to RD falling edge                                                                                                                                                                                                                                     | 10                     |     |     | ns   |

| t <sub>h3</sub>        | Hold time, BYTE or BUS18/16 transition to RD falling edge                                                                                                                                                                                                                                      | 10                     |     |     | ns   |

| t <sub>dis</sub>       | Disable time, RD high (CS high for read cycle) to 3-stated data bus                                                                                                                                                                                                                            |                        |     | 30  | ns   |

| t <sub>d5</sub>        | Delay time, BUSY low to MSB data valid delay                                                                                                                                                                                                                                                   |                        |     | 0   | ns   |

| t <sub>d6</sub>        | Delay time, CS rising edge to BUSY falling edge                                                                                                                                                                                                                                                | 50                     |     |     | ns   |

| t <sub>d7</sub>        | Delay time, BUSY falling edge to CS rising edge                                                                                                                                                                                                                                                | 50                     |     |     | ns   |

| t <sub>su5</sub>       | BYTE transition setup time, from BYTE transition to next BYTE transition, or BUS18/16 transition setup time, from BUS18/16 to next BUS18/16.                                                                                                                                                   | 50                     |     |     | ns   |

| t <sub>su(ABORT)</sub> | Setup time from the falling edge of $\overline{CONVST}$ (used to start the valid conversion) to the next falling edge of $\overline{CONVST}$ (when $CS = 0$ and $\overline{CONVST}$ are used to abort) or to the next falling edge of $\overline{CS}$ (when $\overline{CS}$ is used to abort). | 70                     |     | 550 | ns   |

<sup>(1)</sup> All input signals are specified with  $t_r = t_f = 5$  ns (10% to 90% of +VBD) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . (2) See timing diagrams.

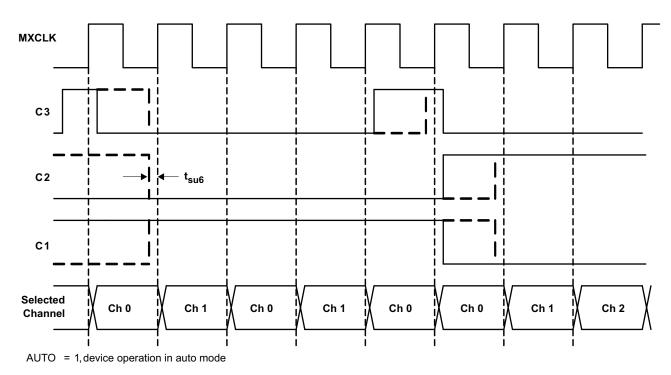

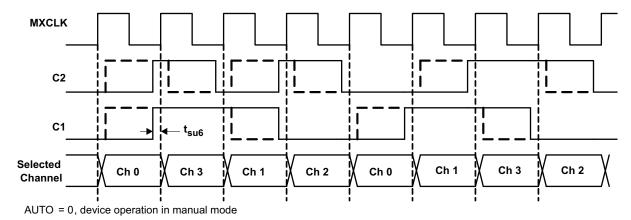

#### **MULTIPLEXER TIMING REQUIREMENTS**

VCC = 4.75 V to 7.5 V, VEE = -3 V to -7.5 V

|                  |                                                                                     | MIN | TYP | MAX | UNIT |

|------------------|-------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>su6</sub> | Setup time C1, C2 or C3 to MXCLK rising edge                                        |     |     | 600 | ns   |

| t <sub>d8</sub>  | Multiplexer and driver settle time ( from MXCLK rising edge to CONVST falling edge) | 600 |     |     | ns   |

Submit Documentation Feedback

All timing are measured with 20-pF equivalent loads on all data bits and BUSY pins.

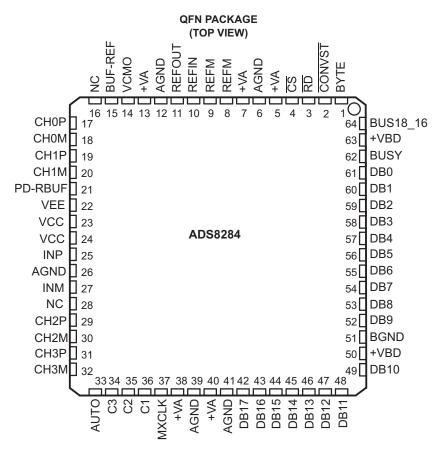

#### **PIN ASSIGNMENTS**

#### **PIN FUNCTIONS**

|        | PIN                    | 1/0   | DESCRIPTION                                                                                                                                               |  |  |  |  |  |  |

|--------|------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NO     | NAME                   | 1/0   | DESCRIPTION                                                                                                                                               |  |  |  |  |  |  |

| MULTIP | MULTIPLEXER INPUT PINS |       |                                                                                                                                                           |  |  |  |  |  |  |

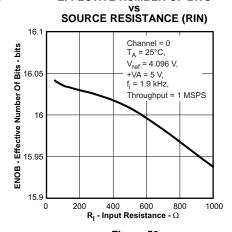

| 17     | CH0P                   | I     | Non-inverting analog input for differential multiplexer channel number 0. Device performance is optimized for $50-\Omega$ source impedance at this input. |  |  |  |  |  |  |

| 18     | СНОМ                   | I     | Inverting analog input for differential multiplexer channel number 0. Device performance is optimized for $50-\Omega$ source impedance at this input.     |  |  |  |  |  |  |

| 19     | CH1P                   | ı     | Non-inverting analog input for differential multiplexer channel number 1. Device performance is optimized for 50-Ω source impedance at this input.        |  |  |  |  |  |  |

| 20     | CH1M                   | ı     | Inverting analog input for differential multiplexer channel number 1. Device performance is optimized for 50-Ω source impedance at this input.            |  |  |  |  |  |  |

| 29     | CH2P                   | ı     | Non-inverting analog input for differential multiplexer channel number 2. Device performance is optimized for 50-Ω source impedance at this input.        |  |  |  |  |  |  |

| 30     | CH2M                   | ı     | Inverting analog input for differential multiplexer channel number 2. Device performance is optimized for $50-\Omega$ source impedance at this input.     |  |  |  |  |  |  |

| 31     | СНЗР                   | ı     | Non-inverting analog input for differential multiplexer channel number 3. Device performance is optimized for 50 ohm source impedance at this input.      |  |  |  |  |  |  |

| 32     | СНЗМ                   | ı     | Inverting analog input for differential multiplexer channel number 3. Device performance is optimized for 50-Ω source impedance at this input.            |  |  |  |  |  |  |

| ADC IN | PUT PINS               |       |                                                                                                                                                           |  |  |  |  |  |  |

| 25     | INP                    | I     | ADC Non inverting input., connect 1-nF capacitor across INP and INM                                                                                       |  |  |  |  |  |  |

| 27     | INM                    | - 1   | ADC Inverting input, connect 1-nF capacitor across INP and INM                                                                                            |  |  |  |  |  |  |

| REFERI | ENCE INPUT/            | OUTPU | T PINS                                                                                                                                                    |  |  |  |  |  |  |

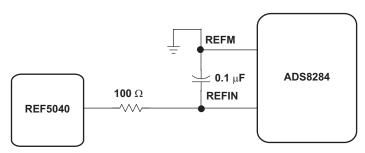

| 8, 9   | REFM                   | - 1   | Reference ground.                                                                                                                                         |  |  |  |  |  |  |

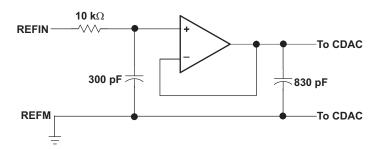

| 10     | REFIN                  | - 1   | Reference Input. Add 0.1-μF decoupling capacitor between REFIN and REFM.                                                                                  |  |  |  |  |  |  |

| 11     | REFOUT                 | 0     | Reference Output. Add 1-μF capacitor between the REFOUT pin and REFM pin when internal reference is used.                                                 |  |  |  |  |  |  |

#### **PIN FUNCTIONS (continued)**

| NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PIN FUNCTIONS (continued) |          |        |                                                                                                   |                          |                                       |                                       |                    |                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------|--------|---------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------|---------------------------------------|--------------------|--------------------|

| 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | NO                        | 1        | I/O    |                                                                                                   |                          | DESCR                                 | RIPTION                               |                    |                    |

| 15   BUF-REF   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                           |          | 0      | This pin outputs PEEIN/2 and can be used to get common mode voltage of differential angles inputs |                          |                                       |                                       |                    |                    |