# 4-BIT COUNTER/LATCH, SEVEN-SEGMENT LED/LAMP DRIVERS

NOVEMBER 1971-REVISED DECEMBER 1983

#### • Choice of Driver Outputs:

SN54143 and SN74143 have 15 mA Constant-Current Outputs for Driving Common-Anode LED's such as TIL302 or TIL303 without Series Resistors

SN54144 and SN74144 Drive High-Current Lamps, Numitrons<sup>†</sup>, or LED's from Saturated Open-Collector Outputs

#### Universal Logic Capabilities

Ripple Blanking of Extraneous Zeros Latch Outputs Can Drive Logic Processors Simultaneously

Decimal Point Driver Is Included

#### Synchronous BCD Counter Capability Includes:

Cascadable to N-Bits

Look-Ahead-Enable Techniques Minimize Speed Degradation When Cascaded for Large-Word Display

Direct Clear Input

SN54143, SN54144 . . . J OR W PACKAGE SN74143, SN74144 . . . J OR N PACKAGE (TOP VIEW)

TYPES SN54143, SN54144, SN74143, SN74144

| SCEI   | 1 2        | 23 | V <sub>CC</sub><br>PECI |

|--------|------------|----|-------------------------|

| CLR    | ]₃         | 22 | MAX                     |

| RBI    | □₄         | 21 | STRE                    |

| BI     | □5         | 20 | QD                      |

| BI/RBO | □6         | 19 | QC                      |

| DP     | Π٦         | 18 | QB                      |

| dp     | <b>∏</b> 8 | 17 | QA                      |

| d      | []9        | 16 | b                       |

| f      | □10        | 15 | а                       |

| е      | □11        | 14 | С                       |

| GND    | <b>1</b> 2 | 13 | g                       |

#### description

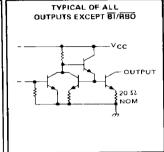

These TTL MSI circuits contain the equivalent of 86 gates on a single chip. Logic inputs and outputs are completely TTL compatible. The buffered inputs are implemented with relatively large resistors in series with the bases of the input transistors to lower drive-current requirements to one-half of that required for a standard Series 54/74 TTL input. The serial-count-enable, actually two internal emitters, is rated as one standard Series 54/74 load. The logic outputs, except RBO, have active pull-ups.

The SN54143 and SN74143 driver outputs are designed specifically to maintain a relatively constant on-level sink current of approximately 15 milliamperes from output "a" through "g" and seven milliamperes from output "dp" over a voltage range from one to five volts. Any number of LED's in series may be driven as long as the output voltage rating is not exceeded.

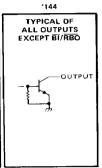

The SN54144 and SN74144 have high-sink-current saturated outputs for driving indicators having voltage ratings up to 15 volts or requiring up to 25 milliamperes drive. The SN54144 sinks 20 milliamperes and the SN74144 sinks 25 milliamperes at an on-level voltage of 0.6 volts across their respective operating temperature ranges.

All inputs are diode-clamped to minimize transmission-line effects, thereby simplifying system design. Maximum clock frequency is typically 18 megahertz and power dissipation is typically 280 milliwatts. The SN54143 and SN54144 are characterized for operation over the full military temperature range of  $-55\,^{\circ}\text{C}$  to  $125\,^{\circ}\text{C}$ ; the SN74143 and SN74144 are characterized for operation from  $0\,^{\circ}\text{C}$  to  $70\,^{\circ}\text{C}$ .

t Trademark of RCA

PRODUCTION DATA

This document contains information currest as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Texas 🌵 Instruments

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

| Functions of the | immutes and | Autoute of | thece | devices a | re as follows: |

|------------------|-------------|------------|-------|-----------|----------------|

|                  |             |            |       |           |                |

| FUNCTION                                                            | PIN NO.                        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLEAR INPUT                                                         | 3                              | When low, resets and holds counter at 0. Must be high for normal counting.                                                                                                                                                                                                                                                                                                                                                                                  |

| CLOCK INPUT                                                         | 2                              | Each positive-going transition will increment the counter provided that the circuit is in the normal counting mode (serial and parallel count enable inputs low, clear input high).                                                                                                                                                                                                                                                                         |

| PARALLEL COUNT<br>ENABLE INPUT (PCEI)                               | 23                             | Must be low for normal counting mode. When high, counter will be inhibited. Logic level must not be changed when the clock is low.                                                                                                                                                                                                                                                                                                                          |

| SERIAL COUNT<br>ENABLE INPUT (SCEI)                                 | 1                              | Must be low for normal counting mode, also must be low to enable maximum count output to go low. When high, counter will be inhibited and maximum count output will be driven high. Logic level must not be changed when the clock is low.                                                                                                                                                                                                                  |

| MAXIMUM COUNT<br>OUTPUT                                             | 22                             | Will go low when the counter is at 9 and serial count enable input is low Will return high when the counter changes to 0 and will remain high during counts 1 through 8. Will remain high (inhibited) as long as serial counterable input is high.                                                                                                                                                                                                          |

| LATCH STROBE<br>INPUT                                               | 21                             | When low, data in latches follow the data in the counter. When high, the data in the latches are held constant, and the counter may be operated independently.                                                                                                                                                                                                                                                                                              |

| LATCH OUTPUTS ( $\Omega_A$ , $\Omega_B$ , $\Omega_C$ , $\Omega_D$ ) | 17, 18, 19, 20                 | The BCD data that drives the decoder can be stored in the 4-bit latch and is available at these outputs for driving other logic and/or processors. The binary weights of the outputs are: $Q_A = 1$ , $Q_B = 2$ , $Q_C = 4$ , $Q_D = 8$ .                                                                                                                                                                                                                   |

| DECIMAL POINT                                                       | 7                              | Must be high to display decimal point. The decimal point is not displayed when this input is low or when the display is blanked.                                                                                                                                                                                                                                                                                                                            |

| BLANKING INPUT                                                      | 5                              | When high, will blank (turn off) the entire display and force RBO low Must be low for normal display. May be pulsed to implement intensity control of the display.                                                                                                                                                                                                                                                                                          |

| RIPPLE-BLANKING<br>INPUT (RBI)                                      | 4                              | When the data in the latches is BCD 0, a low input will blank the entire display and force the $\overline{\mbox{RBO}}$ low. This input has no effect if the data in the latches is other than 0.                                                                                                                                                                                                                                                            |

| RIPPLE-BLANKING<br>OUTPUT (RBO)                                     | 6                              | Supplies ripple blanking information for the ripple blanking input of th next decade. Provides a low if BI is high, or if RBI is low and the data if the latches in BCD 0; otherwise, this output is high. This pin has a resistive pull-up circuit suitable for performing a wire-AND function with an open-collector output. Whenever this pin is low the entire display will be blanked; therefore, this pin may be used as an active-low blanking input |

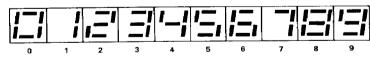

| LED/LAMP DRIVER<br>OUTPUTS<br>(a, b, c, d, e, f, g, dp)             | 15, 16, 14, 9<br>11, 10, 13, 8 | Outputs for driving seven-segment LED's or lamps and their decimal points. See segment identification and resultant displays on followin page.                                                                                                                                                                                                                                                                                                              |

SEGMENT IDENTIFICATION

NUMERICAL DESIGNATIONS-RESULTANT DISPLAYS

TEXAS INSTRUMENTS

POST OFFICE BOX 225012 • DALLAS, TEXAS 75265

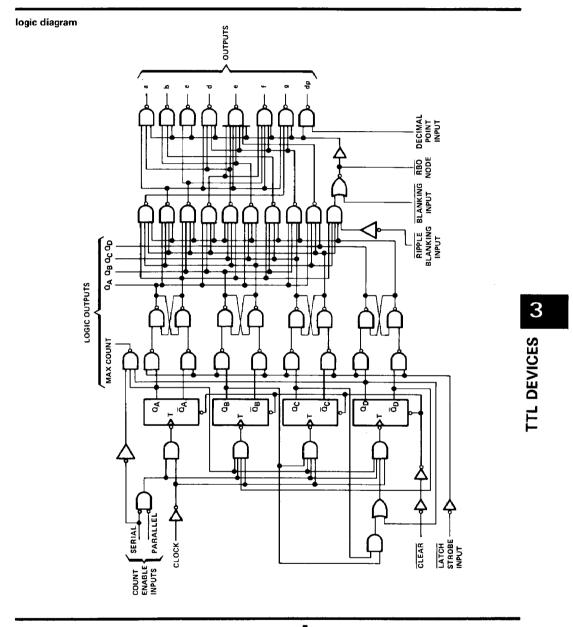

#### schematics of inputs and outputs

'143, '144 EQUIVALENT OF EQUIVALENT OF EACH INPUT EXCEPT BI/RBO vcc. DUTPUT/INPUT ₹ Req 10 kΩ NOM SCEI:  $R_{eq} = 4 k\Omega$  NOM Other inputs:  $R_{eq} = 8 k\Omega$  NOM

143

7 V

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

| Supply voltage, VCC (see Note 1)      |         |         |       | ٠    |      |    |      | . * |      |       |    |    | • |   |   |   | • | • |     |      | . , ,   | v |

|---------------------------------------|---------|---------|-------|------|------|----|------|-----|------|-------|----|----|---|---|---|---|---|---|-----|------|---------|---|

| Input voltage                         |         |         |       |      |      |    |      |     |      |       |    |    |   |   |   |   |   |   |     |      | 5.5 \   | J |

| Off-state voltage at outputs "a" thru | "a" and | d "dp"  | . 144 |      |      |    |      |     |      |       |    |    |   |   |   |   |   |   |     |      | . 15 \  | V |

| Off-state current at outputs "a" thru | "a" and | d "dn"  | 1143  |      |      |    |      |     |      |       |    |    |   |   |   |   |   |   |     |      | 250 µA  | 4 |

| Continuous total power dissipation at | y u     |         | ,     |      |      |    |      |     | lead | , NL  |    | 21 |   |   |   |   |   |   |     |      | 1 4 V   | N |

| Continuous total power dissipation at | tor be  | IOW) /  | UCI   | ee-a | и ге | mp | erat | uie | 1200 | : 140 | ne | -1 | • | • | • |   | • | • |     | · .  | 40-0    |   |

| Operating free-air temperature range: | SN54    | ' Circu | its . |      |      |    |      |     |      |       |    |    |   | ٠ |   | - |   | _ | 55  | C t  | o 125 C | j |

|                                       | SN74    | ' Circu | its . |      |      |    |      |     |      |       |    |    |   |   |   |   |   | - | . ( | D C  | to 70°C | S |

| Storage temperature range             |         |         |       |      |      |    |      |     |      |       |    |    |   |   |   | - |   | _ | 65° | °C t | ە 150°0 | С |

| atorage temperature runge             |         |         |       |      |      |    |      |     |      |       |    |    |   |   |   |   |   |   |     |      |         |   |

NOTES: 1. Voltage values are with respect to network ground terminal.

2. For the SN54143 and SN54144 in the N and W packages, this rating applies at (or below) 80°C free-air temperature. For operation above this temperature, derate linearly at the rate of 11.7 mW/°C for the W package and 14.7 mW/°C for the N package. No derating is required for these devices in the J package.

### recommended operating conditions

|                                        |                                                                         | SN54 | 143, SN | 54144 | SN74 | UNIT |      |      |

|----------------------------------------|-------------------------------------------------------------------------|------|---------|-------|------|------|------|------|

|                                        |                                                                         | MIN  | MOM     | MAX   | MIN  | NOM  | MAX  | UNIT |

| Supply voltage, VCC                    |                                                                         | 4.5  | 5       | 5.5   | 4.75 | 5    | 5.25 | V    |

| On-state voltage at outputs a thru g a | nd dp (*143 only)                                                       | 1    |         | 5     | 1    |      | 5    | V    |

| High-level output current, IOH         | OA, OB, OC, OD                                                          |      |         | -240  |      |      | -240 |      |

|                                        | Maximum count                                                           |      |         | -560  |      |      | -560 | μΑ   |

|                                        | RBO                                                                     | -    |         | -120  | -    |      | -120 |      |

|                                        | Q <sub>A</sub> , Q <sub>B</sub> , Q <sub>C</sub> , Q <sub>D</sub> , RBO |      |         | 4.8   |      |      | 4.8  | mA   |

| Low-level output current, IQL          | Maximum count                                                           |      |         | 11.2  |      |      | 11,2 | 1""  |

|                                        | High logic level                                                        | 25   |         |       | 25   |      |      | ns   |

| Clock pulse width, twiclock)           | Low logic level                                                         | 55   |         |       | 55   |      |      | 1 "" |

| Clear pulse width, tw(clear)           |                                                                         | 25   |         |       | 25   |      |      | ns   |

|                                        | Serial and parallel carry                                               | 301  |         |       | 30†  |      |      | ns   |

| Setup time, t <sub>su</sub>            | Clear inactive state                                                    | 601  |         |       | 601  |      |      |      |

| Operating free-air temperature, TA     | -55                                                                     |      | 125     | 0     |      | 70   | °C   |      |

1The arrow indicates that the rising edge of the clock pulse is used for reference.

Texas Instruments POST OFFICE BOX 225012 . DALLAS, TEXAS 75265

3-548

TTL DEVICES

This Material Copyrighted By Its Respective Manufacturer

### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                                   | PARAM                        | ETER                                                                            | TEST CO                                            | NOITIONS                 | SN54                                             | 143, SN  | 74143 | SN54  | Ī <u> </u> |       |             |

|-----------------------------------|------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------|--------------------------|--------------------------------------------------|----------|-------|-------|------------|-------|-------------|

|                                   |                              |                                                                                 | 1231 00                                            | MDITTONS.                | MIN                                              | TYP      | MAX   | MIN   | TYP!       | MAX   | UNIT        |

| V <sub>IH</sub>                   | High-level input vo          | Itage                                                                           |                                                    |                          | 2                                                |          |       | 2     |            |       | v           |

| VIL                               | Low-level input vol          | Itage                                                                           |                                                    |                          |                                                  |          | 0.8   |       |            | 0.8   | V           |

| VIK                               | Input clamp voltag           | е                                                                               | VCC = MIN,                                         | I <sub>1</sub> = - 12 mA |                                                  |          | - 1.5 |       |            | -1.5  | v           |

| VOH                               | High-level output<br>voltage | Q <sub>A</sub> , Q <sub>B</sub> , Q <sub>C</sub> , Q <sub>D</sub> Maximum count | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> ÷ 0.8 V, |                          | 2.4                                              |          |       | 2.4   |            |       | v           |

| VOL                               | Low-level output<br>voltage  | OA, OB, OC OD, RBO<br>Maximum count                                             | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, |                          |                                                  |          | 0.4   |       |            | 0.4   | v           |

| VO(off)                           | Off-state output voltage     | Outputs a thruig, dip                                                           | V <sub>CC</sub> = MAX.                             | I <sub>OH</sub> = 250 μA | 7                                                |          |       | 15    |            |       | V           |

| VO(on)                            | On State<br>output voltage   | Outputs a thru g, do                                                            | V <sub>CC</sub> = MIN,                             | See Note 3               |                                                  |          |       |       |            | 0.6   | v           |

| On-state<br>IO{on} output current | Outputs a thruig             | $V_{CC} = MIN$ ,<br>$V_{CC} = 5 V$ ,<br>$V_{CC} = MAX$ ,                        | V <sub>O</sub> = 2 V                               | 9                        | 15<br>15                                         | 22       |       |       |            |       |             |

|                                   | Output dp                    | V <sub>CC</sub> = MIN,<br>V <sub>CC</sub> = 5 V,<br>V <sub>CC</sub> = MAX,      | Vo = 2 V                                           | 4.5                      | 7                                                | 12       |       |       |            | mA    |             |

| կ                                 | Input current at ma          | iximum input voltage                                                            | VCC - MAX.                                         |                          | <del> </del>                                     | <u> </u> | 1     | _     |            |       | mA          |

|                                   |                              | Serial carry                                                                    |                                                    |                          | <del>                                     </del> |          | 40    |       |            | 40    | μА          |

| Iн                                | High-level                   | RBO node                                                                        | VCC - MAX,                                         | Vi = 2.4 V               | -0.12                                            | -0.5     |       | -0.12 | -0.5       |       | mA          |

|                                   | input current                | Other inputs                                                                    |                                                    | •                        | -                                                |          | 20    | 9.12  |            | 20    | "A          |

|                                   |                              | Serial carry                                                                    |                                                    |                          | 1                                                |          | -1.6  |       |            | -1.6  | <del></del> |

| կլ                                | Low level                    | RBC node                                                                        | V <sub>CC</sub> = MAX,                             | V; = 0.4 V,              | $\vdash$                                         | -1.5     | -2.4  |       | - 1.5      | -2.4  | mΑ          |

| input current                     | Other inputs                 | See Note 4                                                                      |                                                    |                          |                                                  | -0.8     |       |       | -0.8       |       |             |

|                                   | Short-circuit                | $Q_A, Q_B, Q_C, Q_D$                                                            |                                                    |                          | 9                                                |          | -27.5 | -9    |            | -27.5 |             |

| los                               | output current               | Maximum count                                                                   | V <sub>CC</sub> = MAX                              | -15                      |                                                  | 55       | - 15  |       | 55         | mΑ    |             |

| lcc                               | Supply current               |                                                                                 | V <sub>CC</sub> = MAX,                             | See Note 5               |                                                  | 56       | 93    | - 12  | 56         | 93    | mA          |

<sup>|</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

| All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

| NOTES: 3. For SNS4144, I<sub>OL</sub> = 20 mA, for SN74144, I<sub>OL</sub> = 25 mA.

| 4. I<sub>IL</sub> at RBO node is tested with BI grounded and RBI at 4.5 V.

| 5. I<sub>CC</sub> is measured after the following conditions are established:

| a) Strobe = RBI = DP = 4.5 V |

| b) Parallel count enable = serial count enable = BI = GND |

| c) Clear ("L") then clock until all outputs are on (\( \subseteq \subs

#### switching characteristics, $V_{CC}$ = 5 V, $T_A$ = 25°C

| PARAMETER :       | FROM<br>(INPUT)    | TO<br>(OUTPUT)               | TEST CONDITIONS                                  | MIN | TYP | МАХ                                              | UNIT                                             |    |

|-------------------|--------------------|------------------------------|--------------------------------------------------|-----|-----|--------------------------------------------------|--------------------------------------------------|----|

| fmax              |                    |                              |                                                  | 12  | 18  |                                                  | MHz                                              |    |

| <sup>t</sup> PLH  | Serial look-ahead  | Maximum count                |                                                  |     | 12  | 20                                               |                                                  |    |

| <sup>t</sup> PH L | Serial look affeau | Waximum count                | C <sub>L</sub> = 15 pF, R <sub>L</sub> = 560 Ω,  |     | 23  | 35                                               | ns                                               |    |

| <sup>T</sup> PLH  | Clock              | ock Maximum count See Note 6 |                                                  | 26  | 40  | <del>                                     </del> |                                                  |    |

| tPHL .            | CIDEK              | Waximan count                |                                                  |     | 29  | 45                                               | ns                                               |    |

| <sup>†</sup> PLH  | Clock              | $Q_A, Q_B, Q_C, Q_D$         |                                                  |     | 28  | 45                                               | <del>                                     </del> |    |

| <sup>t</sup> PHL  |                    | QA, GB, GC, GD               | $C_L = 15 \text{ pF}, R_L = 1.2 \text{ k}\Omega$ |     |     | 38                                               | 60                                               | ns |

| ¹PH L             | tPHL Clear QA.     |                              | See Note 6                                       |     | 57  | 90                                               | пs                                               |    |

<sup>\$</sup> f<sub>max</sub> Maximum clock frequency, tp\_H Propagation delay time, low to-high level output, Propagation delay time, high-to-low level output.

NOTE 6: See General Information Section for load circuits and voltage waveforms.

3-550

#### TYPICAL APPLICATION DATA

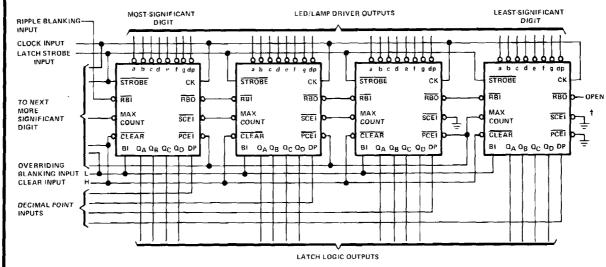

This application demonstrates how the drivers may be cascaded for N-bit display applications. It features:

Synchronous, look-ahead counting

Ripple blanking of leading zeros; blanking of trailing zeros (not illustrated) can also be implemented

TYPES SN54143, SN54144, SN74143, SN74144 4-BIT COUNTER/LATCH, SEVEN-SEGMENT LED/LAMP DRIVERS

Overriding blanking for total suppression or intensity modulation of display

Direct parallel clea

Latch strobe permits counter to acquire next display while viewing current display

<sup>†</sup>The serial count-enable input of the least-significant digit is normally grounded; however, it may be used as a count-enable control for the entire counter (high to disable, low to count) provided the logic level on this pin is not changed while the clock line is low or false counting may result.

### FUNCTION TABLE

|                    |       |       |                 |     | IN | PUTS             |                 |                   |         | OUTPUTS                    |    |   |         |    |       |    |      |      |     |       |     |      |                    |         |

|--------------------|-------|-------|-----------------|-----|----|------------------|-----------------|-------------------|---------|----------------------------|----|---|---------|----|-------|----|------|------|-----|-------|-----|------|--------------------|---------|

| FUNCTION           | CLOCK | CLEAR | LATCH<br>STROBE | RBI | ēī | DECIMAL<br>INPUT | SERIAL<br>CARRY | PARALLEL<br>CARRY | RBI/RBO | MAXIMUM<br>COUNT<br>OUTPUT | OD |   | с<br>СВ | QA | a     |    |      |      |     | IVER: | -   |      | TYPICAL<br>DISPLAY | NOTES   |

| Clear/Ripple Blank |       | ι     | L               | L   | x  | ×                | ×               | ×                 | L       | н                          | L  | L | L       | L  | OFF O | FF | OF F | OFF  | OFF | OFF   | OFF | OFF  | None               | A, E    |

| Blank              |       | н     | L               | Х   | н  | ×                | Х               | x                 | L       | н                          | L  | L | L       | L  | OFF O | FF | OFF  | OFF  | OFF | OFF   | OFF | OFF  | None               | A, D, E |

| Decimal            | 0     | н     | L               | н   | L  | н.               | L.              | L                 | н       | н                          | L  | L | Ļ       | L  | ON C  | NC | ON   | ON   | ON  | ON    | OFF | ON   | J.                 | В       |

|                    | 1     | н     | Ļ               | Н   | Ł  | L                | L               | L                 | н       | н                          | L  | L | L       | Н  | OFF ( | NÇ | ON   | QF F | QFF | QFF   | QFF | QF F | - /-               | В       |

|                    | 2     | н     | L               | Н   | L  | L                | L               | L                 | Н       | н                          | L  | L | Н       | L  | ON 0  | NC | OF F | ٥N   | ON  | OFF   | ON  | OFF  | 2                  | В       |

|                    | 3     | Н     | L               | Н   | ι  | L                | L               | t.                | н       | н                          | L  | L | Н       | Н  | ON C  | DΝ | ON   | ON   | OFF | OFF   | ٥n  | OFF  | 3                  | В       |

|                    | 4     | н     | L               | Н   | Ł  | L                | L               | L                 | н       | н                          | L  | Н | L       | L  | OFF ( | ON | ON   | OFF  | OFF | ОИ    | ON  | OFF  | 4                  | в       |

|                    | 5     | н     | L               | н   | L  | L                | L               | L                 | н       | н                          | L  | н | L       | н  | ON O  | FF | ON   | ON   | OFF | ON    | ON  | OFF  | 5                  | В       |

|                    | 6     | н     | L               | н   | L  | L                | L               | Ł                 | н       | н                          | L  | н | Н       | L  | ON 0  | FF | ON   | ON   | ON  | ON    | ON  | OFF  | 5                  | В       |

|                    | 7     | н     | L               | н   | Ł  | L                | L               | L                 | н       | н                          | L  | н | н       | н  | ON C  | ON | ON   | OFF  | OFF | OFF   | OFF | OFF  | 7                  | 8       |

|                    | 8     | н     | L               | н   | L  | L                | L               | L                 | Н       | н                          | н  | L | L       | L  | ON 0  | NC | ON   | ON   | ON  | ON    | ON  | OFF  | 8                  | В       |

|                    | 9     | н     | L.              | Н   | L  | L                | Ł               | ι                 | н       | L                          | н  | L | L       | Н  | ON 0  | NC | ON   | ON   | OFF | ON.   | ΟN  | OFF  | 9                  | В       |

|                    | 0     | н     | L               | н   | L  | L                | L               | L                 | н       | Н                          | L  | L | L       | L  | ON C  | NC | ON   | ON   | ON  | ON    | OFF | OFF  | 8                  | B, C    |

|                    | 1     | н     | L               | н   | L  | L                | L               | L                 | н       | н                          | L  | L | L       | н  | OFF ( | NC | ON   | OFF  | OFF | OFF   | OFF | OFF  | ;                  | В       |

|                    | 2     | н     | L               | н   | L  | L                | L               | L                 | н       | н                          | L  | L | Н       | L  | ON (  | NC | OF F | ON   | ΟN  | OFF   | ON  | OFF  | Ē                  | В       |

|                    | 3     | н     | L               | н   | Ł  | L                | L               | L                 | н       | н                          | L  | L | ч       | Н  | ON C  | DΝ | ON   | ON   | OFF | OFF   | ON  | OFF  | 3                  | В       |

|                    | 4     | н     | L               | Н   | Ł  | L                | L               | L                 | н       | н                          | Ļ  | Н | L       | L  | QFF ( | ΝC | ON   | QF F | OFF | ON    | ON  | OFF  | '-;'               | 8       |

|                    | 5     | н     | Н               | н   | L  | L                | L               | L                 | Н       | Н                          | Ł  | Н | L       | н  | ON O  | FF | ON   | ON   | OFF | ON    | ON  | OFF  | 11                 | В       |

| Latch              | 6     | н     | н               | Н   | L  | L                | L               | L                 | Н       | н                          | L  | н | L       | н  | ON O  | FF | ΟN   | ON   | OFF | ON    | ON  | OFF  | 5                  | 8       |

| Latch              | 7     | н     | н               | н   | L  | L                | L               | L                 | н       | Н                          | L  | Н | L       | Н  | ON O  | FF | ON   | ON   | OFF | ON    | ON  | OFF  | 7                  | В       |

|                    | 8     | н     | L               | н   | L  | L                | L               | L                 | н       | н                          | Н  | L | L       | L  | ON C  | DΝ | ON   | ON   | ON  | ON    | ON  | OFF  | 8                  | В       |

|                    | 9     | Н     | 1               | Н   | L. | L                | L               | L                 | н       | Ĺ                          | н  | L | L       | н  | ON C  | NC | ON   | ON   | OFF | ON    | ON  | OFF  | 3                  | 8       |

| Ripple Blank       | 0     | н     | L               | L   | х  | L                | L               | L                 | L       | н                          | L  | L | L       | L  | OFF O | FF | OFF  | OFF  | OFF | OFF   | OFF | OFF  | None               | A, B. E |

NOTES: A. 福朗/南西 is wire-AND logic serving as ripple blanking input (福町) and/or ripple blanking output (南西).

B. The blanking input (BI) must be low when functions DECIMAL/0 through 20/RIPPLE BLANK are desired.

C. The ripple-blanking input (RBI) must be open or high to display a zero during the decimal 0 input.

D. When a high logic level is applied directly to the blanking input (81) all segment outputs are off regardless of any other input

E. When the ripple-blanking input ( $\overline{

m RBI}$ ) and outputs  $m Q_A$  through  $m Q_D$  are at a low logic level, all segment outputs are off and the ripple-blanking output (RBO) goes to a low logic level (response condition).

TYPES SN54143, SN54144, SN74143, SN74144 4-BIT COUNTERILATCH, SEVEN-SEGMENT LEDILAMP DRIVERS

SEGMENT IDENTIFICATION

TEXAS

INSTRUMENTS

POST OFFICE 80X 225012 • DALLAS, TEXAS, 78286

**TTL DEVICES**